在转换器领域,说起风头正盛的产品,不能不提射频ADC。关于使用RF ADC的优势,以及如何使用它们进行设计并以高的速率捕获数据,人们进行了大量的讨论。

但是,人们似乎忘了一件事情,即低直流信号。高性能ADC之前的输入配置或者前端设计,对于实现所需的系统性能非常关键。通常重点在于捕获宽带频率,例如大于1 GHz的宽带频率。然而,在某些应用中,也需要直流或近直流信号,并且受到最终用户的欢迎,因为它们也可以传输重要信息。因此,通过优化整体前端设计来捕获直流和宽带信号需要直流耦合前端,该直流耦合前端一直连接到高速转换器。

考虑到应用的本质,将需要开发一个有源前端设计,因为用于将信号耦合到转换器的无源前端和巴伦本身就已交流耦合。接下来我们以实际系统解决方案为例,概述共模信号的重要性,以及如何正确对放大器前端进行电平转换。

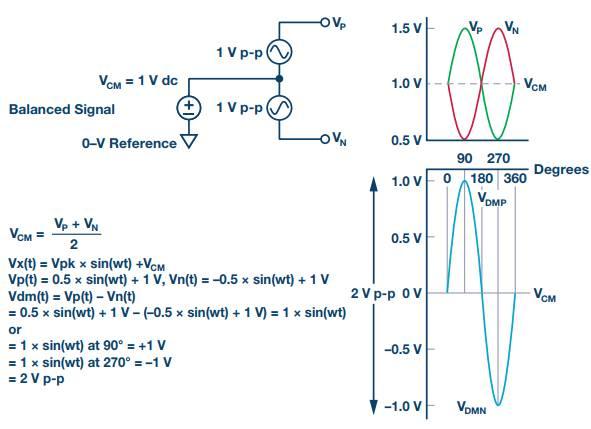

共模

图1显示了转换器如何查看差模与共模信号。CM电压只是信号移动的中点—参见图1。

图1. 差模与共模信号示例

您也可以将其视为新中点或零代码—放大器,通常通过一个VOCM 引脚或类似的器件,在输出端建立CM。不过要小心,这些引脚也有一定的电流和电压范围要求。最好查阅一下放大器数据手册,并且/或者使用不会使电路内部的任何相邻电路或基准点负荷过重的稳定偏置点。不要只是分接一个转换器的基准电压引脚(VREF),它通常是转换器满量程的一半。可能无法提供充分的高精度偏置。谨慎起见,也应查阅转换器数据手册上的引脚技术规格。一般而言,电阻容差1%的简单分压器和/或缓冲器驱动器之类,可正确设置放大器的CM偏置。

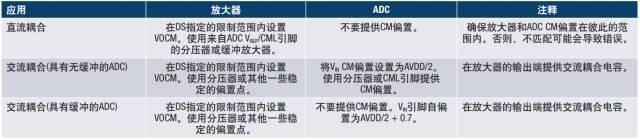

在下面表1中简要列出了如何连接每个应用的放大器和转换器。

表1. 共模矩阵

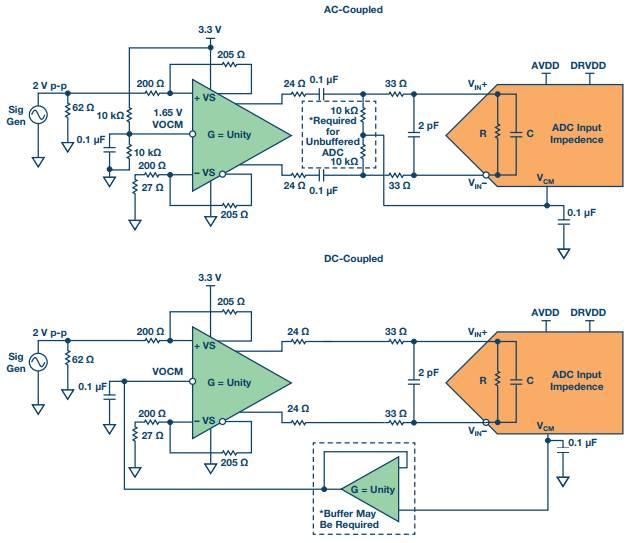

图2显示了一些正确的电路示例。

图2. 用于放大器/转换器前端的交流耦合与直流耦合应用示例

共模:已断开

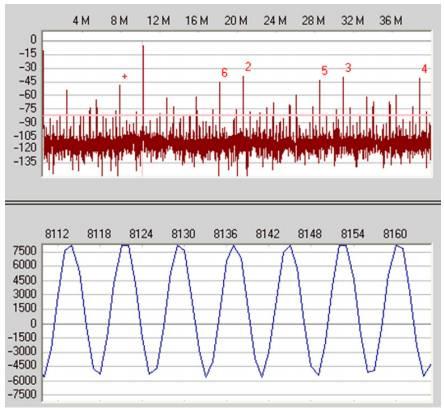

如果未提供或保持共模偏置,转换器将产生增益和失调误差,使获取的总体测量性能下降。简单地说—转换器输出将如图3所示,或者略有变化。

图3. 放大器和转换器之间的CM不匹配

输出频谱的形态将与过载满量程输入相似。这意味着转换器的零点偏离中心,不是最优。你可能会发现转换器会较早削波或者达不到转换器的满量程。但是,由于转换器开始使用1.8 V电源和更低的电源,这一问题变得更为严重。这意味着模拟输入的CM偏置为0.9 V或AVDD/2。并非所有的单电源放大器都支持这样的低共模电压,同时还保持相对较好的性能。

但是,并不是任何旧款放大器都能使用,因为裕量可能非常受限,并且内部晶体管可能会开始塌陷。如果将双电源与放大器配合使用,大多数情况下应该会有充足的裕量来实现适当的CM偏置。缺点是增加了一个额外的电源—可能不标准的负电源,这意味着更多的器件和更高的成本。简单的反相器电路有助于解决这一问题。

将器件连接起来

了解共模和直流耦合之后,我们可以开始组建信号解决方案。例如,ADL5567是双通道差分放大器,增益为20 dB。它具有4.8 GHz带宽,适合连接GSPS ADC,例如AD9625,这是12位、2.5 GSPS转换器,具有JESD204B 8通道接口。图4所示为整体设置框图。

图4. 直流到WB 放大器/转换器信号链示例

在显示的该配置中,前端接口针对宽带采样进行了优化,同时保留信号的直流成分。由于器件为+5.5 V耐压。该设计使用+3.3 V 和−2 V AVDD 分离电源。这使得放大器的输出端和ADC的输入端之间共模简单对齐,两者均需在AIN+和AIN−保持+0.525 V。同样,注意几个接地使能的放大器引脚功能(VSS),单电源现强制 设置为−2 V供电(新VSS)。

CM电压输出很简单,但是弄清楚放大器输入的共模需求可能有点麻烦。需要为接口做两件事:

1

输入端CM电压需要配置为0 V,否则,驱动放大器失调将使输出轨偏向一侧。这将导致图3所描述的性能问题或更严重,—将出现放大器和转换器信号链交流性能不佳。为此,放大器输入端的每一侧都需要允许电流流向地面,或该直流耦合案例中2 V。因此,在每个放大器输入端添加2.2 kΩ的电阻来抑制失调电流。

工作原理:放大器输出约为0.525 V,放大器输入CM电压为0 V。具有500 Ω的内部反馈电阻和约50 Ω的输入电阻使得它看起来有550 Ω;或在本例中,我们假设一个50 Ω源电阻与100 Ω电阻并联,得到33 Ω。再串联20 Ω增加到53 Ω。这是串联了500 Ω内部反馈电阻或总计553 Ω。也就是形成了500 Ω和53 Ω的0.525 V电阻分压器。反过来,产生了900 μA (或0.525/553)的电流。为将此分流至地面或新VSS或−2 V,添加2.2 kΩ电阻或−2 V/2.2 kΩ = 900 μA。

2

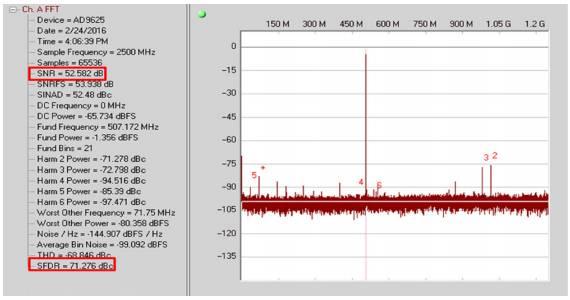

输入为单端输入且需要适当配置来保持最佳性能,同时维持较低偶数阶失真。同样,100 Ω与50 Ω源电阻有效并联,得到33.33 Ω戴维南等效电阻,如前所述。这通常又会反映在VIN节点上,来平衡设备的输入,因为它是单端驱动的。但是,为了改善偶数阶失真,VIN+节点上的20 Ω用于保持所有宽带频率的低失真。这通过使用特定中频约500 MHz完成,—或参见图 5 测试示例。

图5. 典型FFT性能@ 507 MHz AIN @ 2500 MSPS

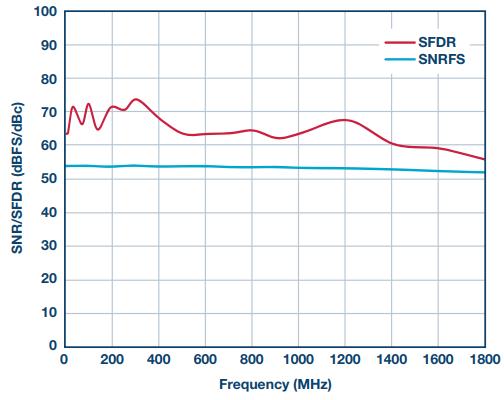

由于它是一个迭代的过程,所以会有些乏味。图6中所示为信号链设计中最高2 GHz输入频率的典型交流频率扫描性能。

图6. 典型交流频率扫描性能@ 2500 MSPS

值得注意的是,添加了5.1 nH电感与电源的正供电轨输入串联。这有助于通过捕捉和再循环放大器内部的这些不平衡电流来再次提高偶数阶线性度性能与频率。

最后,需要针对放大器和ADC之间的前端BW优化接口。这通常 也以迭代的方式完成。但是,对于两个IC之间某些值的设置有 几点需注意。为了在接口中获得最佳BW,请遵循以下规则——

- 根据经验和/或ADC数据手册建议,选择一个反冲电阻器(RKB),(本例中为Ω),通常介于5 Ω和36 Ω之间。

- 选择放大器外部串联电阻(RA)。如果放大器差分输出阻抗在100 Ω至200 Ω范围内,RA应小于10 Ω。如果放大器输出阻抗为12 Ω或更低,RA应介于5 Ω和36 Ω之间。此时,为ADL5567选择10 Ω串联电阻和阻抗为10 Ω的差分输出。

- 放大器输出的串联与并联总电阻应与放大器的表征负载(RL)接近。这里,图4电路中为160 Ω,或2 RA + 2 RKB + RADC = 20 +40 + 100。ADL5567具有200 Ω的RL,所以如果设计值偏离放大器的RL特性值太多,线性度性能可能出现偏差。

- 将内部ADC电容CADC添加至10 Ω串联电阻后的并联电容,来帮助完成内部ADC采样网络反冲。这也提供了软低通滤波来减少任何折回带内的宽带谐波。

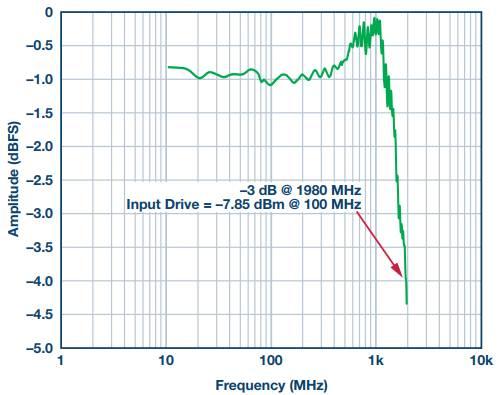

使用上述标准开发出2 GHz通带平坦度响应产品,以捕捉1st和2nd奈奎斯特区内的频率,假设采样速率为2.5 GSPS。该设计的输入 驱动规格将为−8 dBm或252 mV p-p,假设在100 MHz基准频率下具有50 Ω输入阻抗。这是放大器输入要求转换器达到满量程的输入满量程电平。

图7. 典型通带平坦度性能和输入驱动电平

在任何直流耦合设计中,忽略转换器的共模输入电压规格均可引起严重问题。如果使用了多个级别,信号链中的共模水平必须保持一致,以防止两个组件相互冲突。如果未正确耦合,其中一个将经常在各级间取胜,产生虚假测量。对于交流耦合应用,需在两级之间使用一个耦合电容来打破这种共模不匹配。这样设计才能够优化放大器输出和ADC输入的偏置。否则,系统设计中需考虑双电源或电平转换电路,如以上直流耦合设计中的描述。

上一篇:实用篇:宽带密码忘了怎么办?

下一篇:移动的宽带网络为什么要限制迅雷?

2020-07-26 09:11:45

2020-07-26 09:11:45